# MT3332 GNSS Host-Based Solution Data Sheet

Version: 0.01 Release date: 2011-12-20

© 2008 - 2012 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc. Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

# **Document Revision History**

| Revision | Date       | Author   | Description     |

|----------|------------|----------|-----------------|

| 0.01     | 2011/11/19 | Loris Li | Initial version |

# **Table of Contents**

| Docu  | ment    | Revision History                       | 2          |

|-------|---------|----------------------------------------|------------|

| Table | e of Co | ontents                                | 3          |

| 1     | Syste   | em Overview                            | 5          |

|       | 1.1     | General descriptions                   | 5          |

|       | 1.2     | Features                               | 6          |

| 2     | Pin A   | Assignment and Descriptions            | 7          |

|       | 2.1     | Pin assignment (top view)              | 7          |

|       | 2.2     | Pin descriptions                       | 8          |

| 3     | Bloc    | k Diagrams                             | 12         |

|       | 3.1     | Architecture of single-chip receiver   | 12         |

|       | 3.2     | Functional block diagram (RF part)     |            |

| 4     | MT33    | 332 RF Part                            | 13         |

|       | 4.1     | LNA/Mixer                              | 13         |

|       | 4.2     | VCO/Synthesizer                        | 13         |

|       | 4.3     | LPF                                    | 13         |

|       | 4.4     | ADC                                    | 13         |

| 5     | MT33    | 332 Digital Part                       | 14         |

|       | 5.1     | Boot ROM                               | 14         |

|       | 5.2     | Battery backed-up memory               | 14         |

|       | 5.3     | SMPS                                   | 15         |

|       | 5.4     | Timer function                         | 15         |

|       | 5.5     | GPIO in RTC domain                     | 15         |

|       | 5.6     | Low power detection                    |            |

|       | 5.7     | Clock module                           | 15         |

|       | 5.8     | Reset controller                       |            |

|       | 5.9     | Host interface                         |            |

|       |         | 5.9.1 UART                             |            |

|       |         | 5.9.2 SPI                              |            |

|       |         | 5.9.3 I2C                              |            |

|       |         | Interrupt control unit                 |            |

|       | 5.11    |                                        |            |

|       |         | PPS                                    |            |

|       |         | ECLK                                   |            |

|       |         | SYNC                                   |            |

| _     |         | Power scheme                           |            |

| 6     |         | trical Characteristics                 |            |

|       | 6.1     | DC characteristics                     |            |

|       |         | 6.1.1 Absolute maximum ratings         |            |

|       |         | 6.1.2 Recommended operating conditions | 22         |

| Media | Tek Co  | onfidential © 2012 MediaTek Inc. Pag   | ge 3 of 35 |

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

|       | 6.1.3  | General DC characteristics                                                    | 23   |

|-------|--------|-------------------------------------------------------------------------------|------|

|       | 6.1.4  | DC electrical characteristics for 2.8 volts operation                         | 23   |

|       | 6.1.5  | DC electrical characteristics for 1.8 volts operation                         | 23   |

|       | 6.1.6  | DC electrical characteristics for 1.1 volts operation (for FORCE_ON and 32K_O | )UT) |

|       |        |                                                                               | 24   |

| 6.2   | Analo  | g related characteristics                                                     | 24   |

|       | 6.2.1  | SMPS DC characteristics                                                       | 24   |

|       | 6.2.2  | TCXO LDO DC characteristics                                                   | 24   |

|       | 6.2.3  | TCXO SWITCH DC characteristics                                                | 25   |

|       | 6.2.4  | 1.1 volts core LDO DC characteristics                                         | 25   |

|       | 6.2.5  | 1.1 volts RTC LDO DC characteristics                                          | 25   |

|       | 6.2.6  | 32 KHz crystal oscillator (XOSC32)                                            | 25   |

| 6.3   | RF re  | lated characteristics                                                         | 26   |

|       | 6.3.1  | DC electrical characteristics for RF part                                     | 26   |

|       | 6.3.2  | RX chain (GPS-ONLY)                                                           | 26   |

|       | 6.3.3  | RX chain (GPS+BEIDOU mode)                                                    | 27   |

|       | 6.3.4  | RX chain (GPS+GLONASS mode)                                                   | 28   |

|       | 6.3.5  | Crystal oscillator (XO)                                                       | 29   |

| Inter | face C | haracteristics                                                                | 30   |

| 7.1   | RS-23  | 32 interface timing                                                           | 30   |

| 7.2   |        | terface timing                                                                |      |

| 7.3   |        | terface timing                                                                |      |

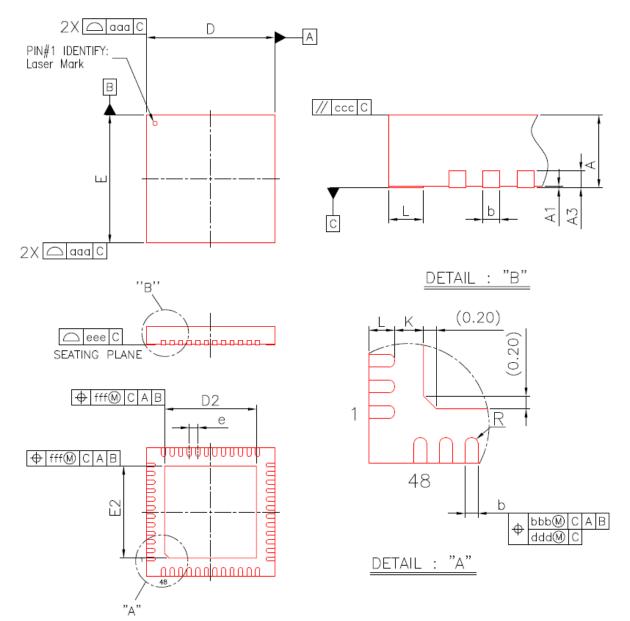

| Pack  | age De | escription                                                                    | 32   |

| 8.1   | -      | nark                                                                          |      |

| 8.2   | -      | ge dimensions                                                                 |      |

| 0.2   |        |                                                                               | 55   |

# **Lists of Figures**

7

8

| Figure 3-1: MT3332 system block diagram                     | 12 |

|-------------------------------------------------------------|----|

| Figure 3-2: MT3332 RF functional block diagram              |    |

| Figure 5-1: RTC with internal RTC LDO application circuit 1 |    |

| Figure 5-2: RTC with internal RTC LDO application circuit 2 | 14 |

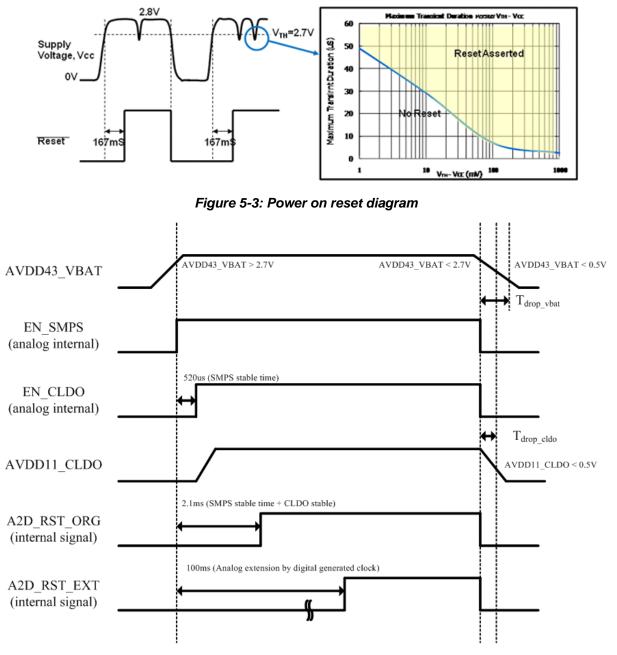

| Figure 5-3: Power on reset diagram                          | 16 |

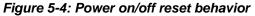

| Figure 5-4: Power on/off reset behavior                     | 16 |

| Figure 5-5: Flow diagram of SYNC function                   | 18 |

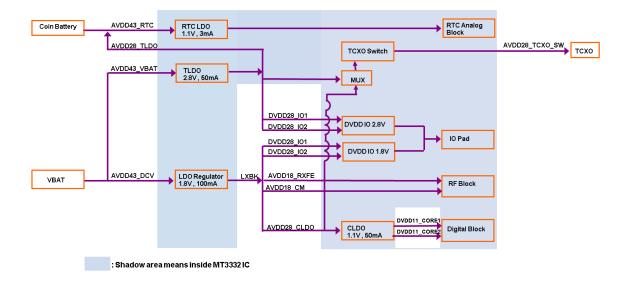

| Figure 5-6: Power supply connection (low power)             | 19 |

| Figure 5-7: Power supply connection (low cost)              | 20 |

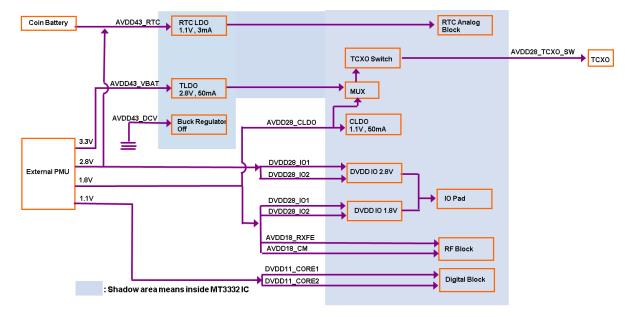

| Figure 5-8: Power supply connection (external LDO)          | 20 |

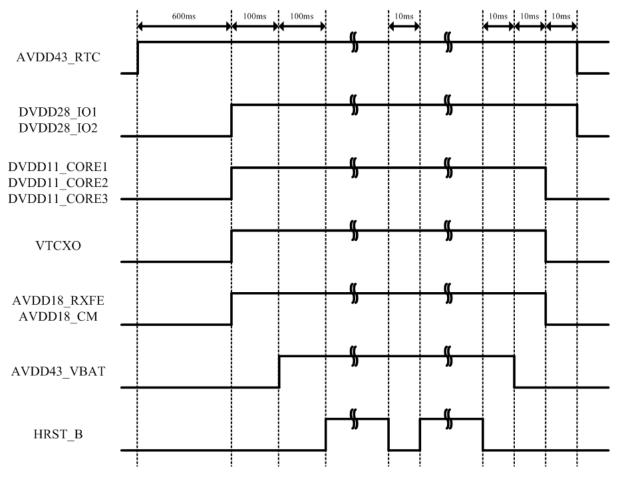

| Figure 5-9: Power on/off sequence for external LDO mode     | 21 |

| Figure 7-1: Timing diagram of RS-232 interface              | 30 |

| Figure 7-2: Timing diagram of SPI interface                 |    |

| Figure 7-3: Timing diagram of HOST I2C interface            |    |

# **1** System Overview

### **1.1 General descriptions**

MT3332 is a high-performance single-chip GPS solution which includes on-chip CMOS RF and digital baseband. It is able to achieve the industry's highest level of sensitivity, accuracy and Time-to-First-Fix (TTFF) with the lowest power consumption in a small-footprint lead-free package. Its small footprint and minimal BOM requirement provide significant reductions in the design, manufacturing and testing resource required for portable applications.

With built-in LNA to reach total NF to TBD dB, you can eliminate antenna requirement and do not need external LNA. With its on-chip image-rejection mixer, the spec of external SAW filter is alleviated. With an on-chip automatic center frequency calibration band pass filter, an external filter is not required. The on-chip power management design allows MT3332 to be easily integrated into your system without extra voltage regulator. With both linear and a highly efficient switching type regulator embedded, MT3332 allows direct battery connection and does not need any external LDO, which gives customers plenty of choices for the application circuit.

Up to 12 multi-tone active interference cancellers (ISSCC2011 award) offer you more flexibility in system design. The integrated PLL with Voltage Controlled Oscillator (VCO) provides excellent phase noise performance and fast locking time. A battery backed-up memory and a real-time clock are also provided to accelerate acquisition at the system restart-up.

MT3332 supports up to 210 PRN channels. With 99 search channels and 33 simultaneous tracking channels, MT3332 acquires and tracks satellites in the shortest time even at indoor signal levels. MT3332 supports various location and navigation applications, including autonomous GPS, GLONASS, GALILEO, BEIDOU(after ICD released), SBAS ranging (WAAS, EGNOS, GAGAN, and MSAS), QZSS, DGPS (RTCM) and AGPS.

Through MT3332's excellent low-power consumption characteristic (acquisition TBD mW, track TBD mW), power sensitive devices, especially portable applications, you will not need to worry about the operating time anymore and can have more fun. Combined with many advanced features including AlwaysLocate<sup>TM</sup>, EASY<sup>TM</sup>, HotStill<sup>TM</sup>, EPO<sup>TM</sup> and logger function, MT3332 provides always-on position with minimal average power consumption. The great features provide you supreme experiences for portable applications such as DSC, cellular phone, PMP, and gaming devices.

### **1.2 Features**

- Specifications

- 33 tracking / 99 acquisition-channel GPS/GLONASS/GALILEO/BEIDOU receiver

- Supports up to 210 PRN channels

- Supports multi-GNSS incl. QZSS, SBAS ranging

- Supports

WAAS/EGNOS/MSAS/GAGAN

- 12 multi-tone active interference cancellers (ISSCC2011 award)

- RTCM ready

- Indoor and outdoor multi-path detection and compensation

- Supports FCC E911 compliance and A-GPS

- Max. fixed update rate up to 10 Hz

- Advanced software features

- AlwaysLocate<sup>TM</sup> advanced location awareness technology

- EPO<sup>™</sup>/HotStill<sup>™</sup> orbit prediction

- Reference oscillator

- TCXO

- Frequency: 16.368 MHz, 12.6 ~ 40.0 MHz

- Frequency variation: ±2.5 ppm

- Crystal

- Frequency: 26 MHz, 12.6 ~ 40.0 MHz

- Frequency accuracy: ±10 ppm

- RF configuration

- SoC, integrated in single chip with CMOS process

- Pulse-per-second (PPS) GPS time reference

- Adjustable duty cycle

- Typical accuracy: ±10 ns

- Power scheme

- A 1.8 volts SMPS build-in SOC

- Direct lithium battery connection (2.8 ~ 4.3 volts)

- Self build 1.1 volts RTC LDO, 1.1 volts core LDO, and 2.8 volts TCXO LDO

- Build-in reset controller

MediaTek Confidential

- Does not need of external reset control IC

- Internal real-time clock (RTC)

- 32.768 KHz ± 20 ppm crystal

- 1.1 volts RTC clock output

- Supports external pin to wake up MT3332

- Serial interface

- 3 UARTs

- SPI

- I2C

- GPIO interface (up to 16 pins)

- Superior sensitivities

- Acquisition: -148 dBm (cold) / -163 dBm (hot)

- Tracking: -165 dBm

- Ultra-low power consumption (GPS only / GPS+GLONASS)

- Acquisition: TBD/TBD mW

- Tracking: TBD/TBD mW

- AlwaysLocate<sup>™</sup>: TBD/TBD mW

- Package

- QFN: 6mm x 6mm, 48 ball

- Slim hardware design

- 9 passive external components

- Single RF Front-End for Multi-GNSS frequency bands

- Compatibility

- Pin-to-pin compatible to MT3336

# 2 Pin Assignment and Descriptions

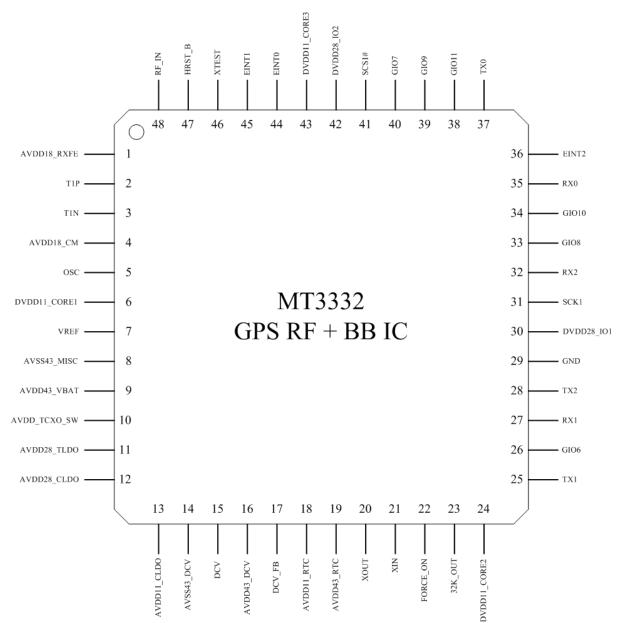

# 2.1 Pin assignment (top view)

© 2012 MediaTek Inc.

# 2.2 Pin descriptions

| Pin#    | Symbol                                        | Туре                                                            | Description                                                                                                                                                                                                          |

|---------|-----------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System  | interface (2 pins)                            |                                                                 |                                                                                                                                                                                                                      |

| 47      | HRST_B                                        | 2.8V LVTTL input default pull-up, SMT                           | System reset. Active low                                                                                                                                                                                             |

| 46      | XTEST                                         | 2.8V LVTTL input<br>default pull-down,<br>SMT                   | Test mode. <i>Must keep low in normal mode.</i>                                                                                                                                                                      |

| Periphe | ral interface (8 pins)                        |                                                                 |                                                                                                                                                                                                                      |

| 35      | RX0/MM_I2CC/H_SPI_SI                          | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial input for UART 0<br>Default: pull-up<br>Default: 8mA driving                                                                                                                                                  |

| 37      | TX0/MM_I2CD/H_SPI_SO                          | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial output for UART 0<br>Default: pull-up<br>Default: 8mA driving                                                                                                                                                 |

| 27      | RX1/H_SPI_SCK/CTS0/MM_<br>I2CC/CXO_TSENS/GIO0 | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial input for UART 1<br>Default: pull-up<br>Default: 8mA driving                                                                                                                                                  |

| 25      | TX1/TXIND/RTS0/MM_I2CD/<br>CXO_CS/GIO1        | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial output for UART 1<br>Default: pull-up<br>Default: 8mA driving                                                                                                                                                 |

| 32      | RX2/SPI_SI/JDI/DBG_RX/BS<br>I_CK/GIO2         | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial input for UART 2<br>Default: pull-up<br>Default: 8mA driving                                                                                                                                                  |

| 28      | TX2/SPI_SO/DBG_TX/GIO3                        | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | Serial output for UART 2<br>Default: pull-up<br>Default: 8mA driving<br>Strap pin tcxo_sw_sel<br>1'b0: AVDD_TCXO_SW output 1.8V<br>1'b1: AVDD_TCXO_SW output 2.8V                                                    |

| 31      | SCK1/SPI_SCK/GIO4                             | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | SPI clock output<br>Default: pull-up<br>Default: 8mA driving<br>Strap pin clk_sel[0]<br><b>Clk_sel[1:0] Mode</b><br>2'b00: XTAL mode<br>2'b01: External clock mode<br>2'b10: TCXO mode<br>2'b11: 16.368MHz TCXO mode |

| Pin#    | Symbol                                      | Туре                                                            | Description                                                                                                                                                          |

|---------|---------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41      | SCS1#/SPI_SCS#/BSI_DAT<br>A/SYNC_PULSE/GIO5 | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | SPI slave selection 1<br>Default: pull-up<br>Default: 8mA driving<br>Strap pin clk_sel[1]                                                                            |

| Debugg  | ing interface (6 pins)                      |                                                                 |                                                                                                                                                                      |

| 26      | BSI_CK/MM_I2CC/ECLK/GI<br>O6                | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO6<br>Default: pull-down<br>Default: 8mA driving                                                                                                                  |

| 40      | BSI_CS/MM_I2CD/DUTY_C<br>YCLE/PPS/GIO7      | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO7<br>Default: pull-down<br>Default: 8mA driving                                                                                                                  |

| 33      | FRAME_SYNC/DBG_RX/GI<br>O8                  | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO8.<br>Default: pull-down<br>Default: 8mA driving                                                                                                                 |

| 39      | PPS/DBG_TX/GIO9                             | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO9<br>Default: pull-up<br>Default: 8mA driving<br>Strap pin host_sel[0]<br>Host_sel[1:0] Interface<br>2'b00: I2C<br>2'b01: UART MEIF<br>2'b10: SPI<br>2'b11: UART |

| 34      | CXO_CS/GIO10                                | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO10<br>Default: pull-up<br>Default: 8mA driving<br>Strap pin host_sel[1]                                                                                          |

| 38      | H_SPI_SCS#/CXO_TSENS/<br>SYNC_PULSE/GIO11   | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | GPIO11<br>Default: pull-up<br>Default: 8mA driving                                                                                                                   |

| Externa | I system interface (3 pins)                 |                                                                 |                                                                                                                                                                      |

| 44      | EINT0/MM_I2CC/BSI_CS/GI<br>O12              | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | External interrupt 0<br>Default: pull-down<br>Default: 8mA driving                                                                                                   |

| 45      | EINT1/MM_I2CD/PPS/BSI_D<br>ATA/GIO13        | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | External interrupt 1<br>Default: pull-down<br>Default: 8mA driving                                                                                                   |

| 36      | EINT2/DBG_RX/PPS/GIO14                      | 2.8V, LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | External interrupt 2<br>Default: pull-up<br>Default: 8mA driving                                                                                                     |

| RTC int | erface (6 pins)                             |                                                                 |                                                                                                                                                                      |

MediaTek Confidential

© 2012 MediaTek Inc.

| Pin#    | Symbol        | Туре                                                           | Description                                                                                                                                      |

|---------|---------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 19      | AVDD43_RTC    | Analog power                                                   | RTC LDO input                                                                                                                                    |

| 18      | AVDD11_RTC    | Analog power                                                   | RTC LDO output                                                                                                                                   |

| 21      | XIN           | Analog input                                                   | RTC 32KHz XTAL input                                                                                                                             |

| 20      | XOUT          | Analog output                                                  | RTC 32KHz XTAL output                                                                                                                            |

| 23      | 32K_OUT/DR_IN | 1.2V LVTTL I/O<br>PPU, PPD, SMT<br>4mA, 8mA, 12mA,<br>16mA PDR | RTC domain GPIO pin, can be<br>programmed to 32KHz clock output or DR<br>wake-up signal input<br>Default: 75K pull-down<br>Default: 16mA driving |

| 22      | FORCE_ON      | 1.2V LVTTL I/O<br>PPU,PPD, SMT                                 | Force to power on this chip.                                                                                                                     |

| RF & an | alog          |                                                                |                                                                                                                                                  |

| 1       | AVDD18_RXFE   | RF power                                                       | 1.8V supply for RF core circuits                                                                                                                 |

| 2       | T1P           | Analog signal                                                  | RF testing signal                                                                                                                                |

| 3       | T1N           | Analog signal                                                  | RF testing signal                                                                                                                                |

| 4       | AVDD18_CM     | RF power                                                       | 1.8V supply for XTAL OSC, bandgap,<br>Thermal sensor and level shifter                                                                           |

| 5       | OSC           | Analog signal                                                  | Input for crystal oscillator or TCXO                                                                                                             |

| 48      | RF_IN         | RF signal                                                      | LNA RF Input pin                                                                                                                                 |

| 6       | DVDD11_CORE1  | Digital power                                                  | Digital 1.1V core power input                                                                                                                    |

| 24      | DVDD11_CORE2  | Digital power                                                  | Digital 1.1V core power input                                                                                                                    |

| 43      | DVDD11_CORE3  | Digital power                                                  | Digital 1.1V core power input                                                                                                                    |

| 30      | DVDD28_IO1    | Digital power                                                  | Digital 1.8/2.8V IO power input                                                                                                                  |

| 42      | DVDD28_IO2    | Digital power                                                  | Digital 1.8/2.8V IO power input                                                                                                                  |

| 29      | GND           | Digital ground                                                 | Digital ground                                                                                                                                   |

| 7       | VREF          | Analog                                                         | Bandgap output pin. Must add 1uF decoupling cap on EVB.                                                                                          |

| 8       | AVSS43_MISC   | Analog ground                                                  | GND pin for buck controller, TCXO LDO and start-up block                                                                                         |

| 9       | AVDD43_VBAT   | Analog power                                                   | TCXO LDO input pin. always be powered<br>by external source. UVLO will detect this<br>PIN to check power status.                                 |

| 10      | AVDD_TCXO_SW  | Analog power                                                   | TCXO power switch output pin                                                                                                                     |

| 11      | AVDD28_TLDO   | Analog power                                                   | TCXO LDO output pin                                                                                                                              |

| 12      | AVDD28_CLDO   | Analog power                                                   | Core LDO input pin. Always powered by external source or SMPS                                                                                    |

| 13      | AVDD11_CLDO   | Analog power                                                   | Core LDO output pin                                                                                                                              |

| 14      | AVSS43_DCV    | SMPS                                                           | SMPS GND pin                                                                                                                                     |

| 15      | DCV           | SMPS                                                           | SMPS output pin                                                                                                                                  |

| 16      | AVDD43_DCV    | SMPS                                                           | SMPS input pin.                                                                                                                                  |

| 17      | DCV_FB        | SMPS                                                           | SMPS feedback pin                                                                                                                                |

Notes:

PPU = Programmable pull-up

PPD = Programmable pull-down

PSR = Programmable slew rate

MediaTek Confidential

© 2012 MediaTek Inc.

Page 10 of 35

PDR = Programmable driving

# **3 Block Diagrams**

# 3.1 Architecture of single-chip receiver

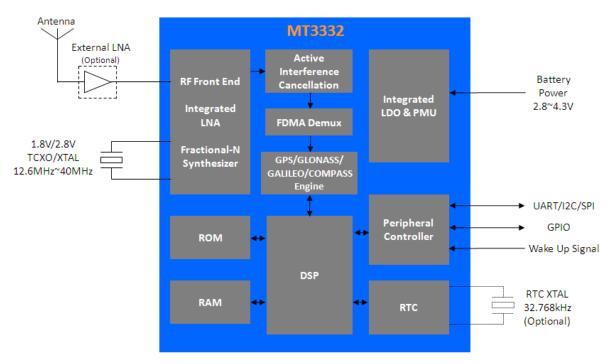

Figure 3-1: MT3332 system block diagram

# 3.2 Functional block diagram (RF part)

#### Figure 3-2: MT3332 RF functional block diagram

# 4 MT3332 RF Part

### 4.1 LNA/Mixer

Upon receiving RF input signal in through either GPS antenna to internal LNA or external antenna and LNA, the mixer down converts the amplified signal (GPS/Galileo=1575.42MHz, Beidou=1561.098-MHz, GLONASS=1601.71-MHz). The current chip provides 2 configurations to choose from, which are high-gain LNA and low-gain LNA. The high-gain LNA is used for low-cost solution without external LNA. The low-gain LNA offers high linearity to allow high external LNA gain, with much worsen noise figure performance. In the application with external LNA, the external LNA gain ranging from 0 to 20 dB is recommended. The down-conversion mixer is single-ended passive mixer with current mode interface between the mixer and multi-modes low pass filter.

# 4.2 VCO/Synthesizer

The entire frequency synthesizer includes crystal oscillator, VCO, divider, phase frequency detector (PFD), charge pump (CP) and loop filter which are all integrated on the MT3332 chip. Upon power-on, VCO is auto-calibrated to its required sub-band. The synthesizer adopts fractional-N sigma-delta PLL topology, which supports 12.6 to 40MHz reference clock frequencies.

# 4.3 LPF

The current-mode LPF supports multiple modes for different GNSS combinations. The LPF also provides 26dB gain-control range, with approximately 2dB per step.

# 4.4 ADC

The differential IF signal is being quantized by a high performance ADC. The sampling clock can be provided from divided clock from LO. The ADC can be programmed between high performance mode (GPS+GLONASS) for high bandwidth, and low performance mode (GPS-ONLY) for lower current consumption.

# 5 MT3332 Digital Part

### 5.1 Boot ROM

The embedded boot ROM provides a function of loading a set of user code through the host interface into SRAM. The host interface (UART/SPI/I2C) is decided by strap control.

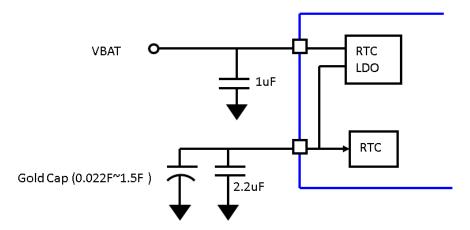

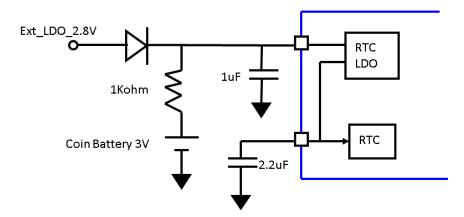

### 5.2 Battery backed-up memory

MT3332 provides very low leakage (about TBD uA in the backup mode) battery backed-up memory, which contains all the necessary GPS information for quick start-up and a small amount of user configuration variables. There is a built-in 1.1 volts LDO for RTC domain and it can be bypassed while an external LDO is applied. The RTC LDO is a voltage regulator having very low quiescent current, and typical quiescent current < TBD uA. The small ceramic capacitor can be used as the output capacitor, and the stable operation region ranges from very light load (~=0) to about TBD mA.

Figure 5-1: RTC with internal RTC LDO application circuit 1

Figure 5-2: RTC with internal RTC LDO application circuit 2

MediaTek Confidential

# 5.3 SMPS

A built-in switching mode power supply provides 1.8 volts power supply for the digital 1.1 volts CLDO and RF input power. In the active mode, SMPS is operated in the PWM mode. In the power saving mode, SMPS is operated with reduced switching frequency in the PFM mode. The recommended L/C value is 1 uH / 4.7 uF.

# 5.4 Timer function

The timer function supports a time tick generation of 31.25 ms resolution. With the 24-bit counter, the period of timer is from 31.25 ms to 524,287 s.

# 5.5 **GPIO in RTC domain**

The "32K\_OUT" pin in RTC domain can output 32.768 KHz clock which can be used to support low clock rate operation mode for some applications or peripherals that need an external clock source. This pin can also be programmed to be an input pin to receive the signal from an external accelerator sensor IC to be the wake-up signal of MT3332 when it is in the low-power mode.

# 5.6 Low power detection

A low power detection circuit is implemented. Whenever the independent power source (AVDD11\_RTC) becomes low voltage, the low power detection circuit will detect this condition and use an indicator signal (output high in normal condition and low in low-power condition) to reflect this condition.

# 5.7 Clock module

The clock module generates all internal clocks required by processor, correlator, internal memory, bus interface and so on. The referenced input clock is generated from the RF block. For system flexibility and maximum power saving, it supports various power management modes.

# 5.8 Reset controller

The built-in reset controller generates reset signals for all digital blocks. It has power-on reset feature and hardware trapping function. The power-on reset level is  $2.7 \pm 0.1$  volts. The software reset function for different circuit blocks are also included for flexible applications.

In Figure 5-4, the voltage drop time  $T_{drop\_vbat}$  and  $T_{drop\_cldo}$  depend on the capacitance connection of their power net. But  $T_{drop\_vbat} > T_{drop\_cldo}$  should be guaranteed for the correct operation of reset behavior during power off sequence. It is strongly recommend using external LDOs without output discharged function or make sure  $T_{drop\_vbat} > 100$  ms.

#### 5.9 Host interface

MT3332 supports 3 different host interfaces, which are UART, SPI, and I2C. The interface used as the host interface is determined by strap pins. Note that SPI and I2C support firmware update only for now.

#### 5.9.1 UART

UART is the abbreviation of "Universal Asynchronous Receiver/Transmitter". MT3332 has 3 full duplex serial ports. It is used for serial data communication. A UART converts bytes of data to and from asynchronous start-stop bit streams represented as binary electrical impulses.

There are several functions in MT3332 related to UART communication, such as UART data transmission/receive and aiding information input from host processor. In general, UART0 is as measurement data output and PMTK command input, UART1 as RTCM input. You can adjust the UART2 port as desired. The receiver (RX) and transmitter (TX) side of every port contains a 16-byte FIFO, but only UART0 has 256 bytes of URAM. The bit rates are selectable and range from 4.8 to 921.6 kbps. UART provides signal or message outputs.

#### 5.9.2 SPI

The serial peripheral interface port manages the communication between digital BB and external devices. MT3332 supports both master and slave modes. Only 4 bytes of register in the master mode can be transferred. The slave has 4-byte-register mode or URAM mode. In the URAM mode, the transmitted and received data size is 256 bytes. The clock phase and clock polarity are selectable. MT3332 supports manual or automatic indicator for data transfer in the slave mode.

#### 5.9.3 I2C

The I2C interface is mainly connected to external devices. MT3332 supports multi-master and slave modes. Both modes have 256-byte URAM mode and 8-byte FIFO mode for transmitting and receiving data. The multi-master mode supports 7-bit and 10-bit address modes up to 400 Kb/s fast mode and 3.4 Mb/s high-speed mode. In additions, MT3332 supports manual or automatic indicator for data transfer in the slave mode. Device addresses in the slave mode are programmable and support fast mode and high-speed mode data transmission and reception.

#### 5.10 Interrupt control unit

The interrupt control unit manages all internal and external sources of interrupts, which include timer, watch-dog, all interfaces such as UART, I2C and SPI and external user interrupt pins. These interrupt sources can be wake-up events in the power saving mode.

#### 5.11 GPIO unit

GPIO is the abbreviation of "General-Purpose Input/Output". MT3332 supports a variety of peripherals through maximum 15 GPIO programmable ports. The unit manages all GPIO lines and supports a simple control interface. GPIO provides signal or message outputs.

# 5.12 PPS

The PPS (Pulse Per Second) signal is provided through designated output pin for many external applications. The pulse is not only limited to being active every second but also allowed to set up the required duration, frequency and active high/low by programming user-defined settings.

# 5.13 ECLK

ECLK is a clock input pin for introducing an external clock signal to MT3332 and obtaining the relation between the external clock and GPS local clock. With precise external clock input, the clock drift of the GPS local clock can be correctly estimated. Therefore, the Doppler search range is narrowed down accordingly. The technology is beneficial to speeding up the satellite acquisition process. Particularly in the cold start case, due to limited priori information about the satellite's location and local clock uncertainty, a receiver will execute a search in full frequency range. Consequently, a longer acquisition time is expected. However, the ECLK technology is able to reduce the frequency uncertainty so that the search process will be completed in a short time. Efficient acquisition and lower power consumption are attained by the ECLK technology.

# 5.14 SYNC

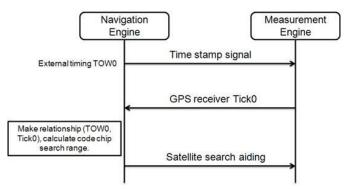

SYNC is a time stamp signal input pin for introducing an external timing to the GPS receiver and obtaining the relation between the external timing and the GPS receiver local timing. With precise external timing input and the established relation, the GPS time of week (TOW) can be correctly estimated in the GPS receiver. The technology is beneficial for time to first fix (TTFF), particularly in weak signal environments. In hot starts, with priori information about the GPS receiver's location and satellite ephemeris data, the GPS receiver uses the correct GPS TOW to accurately predict the signal code chip/phase. Therefore, the code search range can be narrowed down accordingly. Hence, fast TTFF is achieved by the SYNC technology.

Figure 5-5: Flow diagram of SYNC function

# 5.15 Power scheme

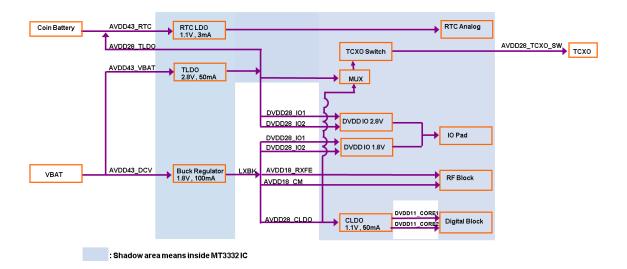

- Internal SMPS is used as the source power of the internal RF/BB LDO. It is also used as 1.8 volts I/O power. The internal SMPS can switch to the LDO mode to supply power to each of the about block

- External LDO or VBAT can be used as the main power. The minimum/maximum input voltage of AVDD43\_VBAT and AVDD43\_DCV is 2.8/4.3 volts.

- The power-on reset voltage threshold of AVDD43\_VBAT is 2.7 ± 0.1 volts. The maximum TLDO drop out voltage at half load (25 mA) is 0.25 volts. If one external LDO is used to provide power to

MT3332, the 3.3 volts external LDO will be recommended after taking TLDO drop-out into consideration.

- The power efficiency in SMPS mode will be better than that in the internal LDO mode.

- I/O supports 1.8 and 2.8 volts. The power comes from SMPS output for 1.8 volts application or TLDO output (AVDD28\_TLDO) for 2.8 volts application.

- TCXO power is from AVDD\_TCXO\_SW with an internal MUX to select 2.8 volts from AVDD28\_TLDO or 1.8 volts from AVDD28\_CLDO by setting up power-on strap.

- RTC LDO input power comes from AVDD28\_TLDO and uses coin battery as the backup battery. A schottky diode is usually used to avoid leakage from coin battery to TLDO.

- Here are 3 power schemes: low power (Figure 5-6), low cost (Figure 5-7) and external PMU (Figure 5-8).

- In Figure 5-8, if 2.8V TCXO is used, AVDD28\_CLDO should be open for saving power.

Figure 5-6: Power supply connection (low power)

# **MEDI/ITEK**

Figure 5-7: Power supply connection (low cost)

Figure 5-8: Power supply connection (external LDO)

Page 21 of 35

# **6** Electrical Characteristics

# 6.1 DC characteristics

#### 6.1.1 Absolute maximum ratings

| Symbol                                       | Parameter                             | Rating      | Unit |

|----------------------------------------------|---------------------------------------|-------------|------|

| AVDD43_DCV                                   | SMPS power supply                     | -0.3 ~ 4.3  | V    |

| AVDD43_VBAT                                  | 2.8 volts TLDO power supply           | -0.3 ~ 4.3  | V    |

| AVDD28_CLDO                                  | 1.1 volts CLDO power supply           | -0.3 ~ 3.6  | V    |

| DVDD28_IO1<br>DVDD28_IO2                     | IO 2.8/1.8 volts power supply         | -0.3 ~ 3.6  | V    |

| DVDD11_CORE1<br>DVDD11_CORE2<br>DVDD11_CORE3 | Baseband 1.1 volts power supply       | -0.3 ~ 1.21 | V    |

| AVDD43_RTC                                   | RTC 1.1 volts LDO power supply        | -0.3 ~ 4.3  | V    |

| AVDD18_RXFE                                  | 1.8 volts supply for RF core circuits | -0.3 ~ 3.6  | V    |

| AVDD18_CM                                    |                                       | -0.3 ~ 3.6  | V    |

| T <sub>STG</sub>                             | Storage temperature                   | -50 ~ +125  | °C   |

| T <sub>A</sub>                               | Operating temperature                 | -45 ~ +85   | °C   |

### 6.1.2 Recommended operating conditions

| Symbol                                       | Parameter                                                | Min. | Тур. | Max. | Unit |

|----------------------------------------------|----------------------------------------------------------|------|------|------|------|

| AVDD43_DCV                                   | SMPS power supply                                        | 2.8  | 3.3  | 4.3  | V    |

| AVDD43_VBAT                                  | 2.8 volts TLDO power supply                              | 2.8  | 3.3  | 4.3  | V    |

| DVDD11_CORE1<br>DVDD11_CORE2<br>DVDD11_CORE3 | 1.1 volts baseband core power                            | 0.99 | 1.1  | 1.21 | V    |

| DVDD28_IO1                                   | 2.8 volts digital I/O power                              | 2.52 | 2.8  | 3.08 | V    |

| DVDD28_IO2                                   | 1.8 volts digital I/O power                              | 1.62 | 1.8  | 1.98 | V    |

| AVDD18_RXFE                                  | 1.35 volts supply for RF core<br>circuits in bypass mode | 1.3  | 1.35 | 1.98 | V    |

| AVDD16_KAFE                                  | 1.8 volts supply for RF core circuits in LDO mode        | 1.62 | 1.8  | 3.08 | V    |

| AVDD18 CM                                    | 1.35 volts supply for common RF block in bypass mode     | 1.3  | 1.35 | 1.98 | V    |

| AVDD18_CM                                    | 1.8V volts supply for common RF block in LDO mode        | 1.62 | 1.8  | 3.08 | V    |

| т                                            | Operating temperature                                    | -40  | 25   | 85   | °C   |

| T <sub>A</sub><br>T <sub>j</sub>             | Commercial junction operating temperature                | 0    | 25   | 115  | °C   |

|                                              | Industry junction operating temperature                  | -40  | 25   | 125  | °C   |

MediaTek Confidential

© 2012 MediaTek Inc.

Page 22 of 35

#### 6.1.3 General DC characteristics

| Symbol          | Parameter                 | Condition          | Min. | Max. | Unit |

|-----------------|---------------------------|--------------------|------|------|------|

| I <sub>IL</sub> | Input low current         | No pull-up or down | -1   | 1    | uA   |

| I <sub>IH</sub> | Input high current        | No pull-up or down | -1   | 1    | uA   |

| l <sub>oz</sub> | Tri-state leakage current |                    | -10  | 10   | uA   |

#### 6.1.4 DC electrical characteristics for 2.8 volts operation

| Symbol          | Parameter                     | Condition                              | Min.       | Тур. | Max.       | Unit |

|-----------------|-------------------------------|----------------------------------------|------------|------|------------|------|

| VDD             | Supply voltage of core power  |                                        | 0.99       | 1.1  | 1.21       | V    |

| VDDIO           | Supply voltage of IO power    |                                        | 2.52       | 2.8  | 3.08       | V    |

| V <sub>IL</sub> | Input lower voltage           | LVTTL                                  | -0.3       | -    | 0.25*VDDIO | V    |

| V <sub>IH</sub> | Input high voltage            |                                        | 0.75*VDDIO | -    | VDDIO+0.3  | V    |

| V <sub>OL</sub> | Output low voltage            | VDDIO = min<br>I <sub>OL</sub> = -2 mA | -          | -    | 0.15*VDDIO | V    |

| V <sub>OH</sub> | Output high voltage           | VDDIO = min<br>I <sub>OH</sub> = -2 mA | 0.85*VDDIO | -    | -          | V    |

| R <sub>PU</sub> | Input pull-up resistance      | VDDIO = typ<br>Vinput = 0 V            | 40         | 85   | 190        | ΚΩ   |

| R <sub>PD</sub> | Input pull-down<br>resistance | VDDIO = typ<br>Vinput = 2.8 V          | 40         | 85   | 190        | KΩ   |

#### 6.1.5 DC electrical characteristics for 1.8 volts operation

| Symbol          | Parameter                     | Condition                              | Min.       | Тур. | Max.       | Unit |

|-----------------|-------------------------------|----------------------------------------|------------|------|------------|------|

| VDD             | Supply voltage of core power  |                                        | 0.99       | 1.1  | 1.21       | V    |

| VDDIO           | Supply voltage of IO power    |                                        | 1.62       | 1.8  | 1.98       | V    |

| VIL             | Input lower voltage           | LVTTL                                  | -0.3       | -    | 0.25*VDDIO | V    |

| V <sub>IH</sub> | Input high voltage            |                                        | 0.75*VDDIO | -    | VDDIO+0.3  | V    |

| V <sub>OL</sub> | Output low voltage            | VDDIO = min<br>I <sub>OL</sub> = -2 mA | -          | -    | 0.15*VDDIO | ۷    |

| V <sub>OH</sub> | Output high voltage           | VDDIO = min<br>I <sub>OH</sub> = -2 mA | 0.85*VDDIO | -    | -          | V    |

| R <sub>PU</sub> | Input pull-up resistance      | VDDIO = typ<br>Vinput = 0 V            | 70         | 150  | 320        | KΩ   |

| R <sub>PD</sub> | Input pull-down<br>resistance | VDDIO = typ<br>Vinput = 1.8 V          | 70         | 150  | 320        | KΩ   |

# 6.1.6 DC electrical characteristics for 1.1 volts operation (for FORCE\_ON and 32K\_OUT)

| Symbol          | Parameter                     | Condition                              | Min.       | Тур. | Max.       | Unit |

|-----------------|-------------------------------|----------------------------------------|------------|------|------------|------|

| VDD             | Supply voltage of core power  |                                        | 0.99       | 1.1  | 1.21       | V    |

| VDDIO           | Supply voltage of IO power    |                                        | 0.99       | 1.1  | 1.21       | V    |

| V <sub>IL</sub> | Input lower voltage           | LVTTL                                  | -0.3       | -    | 0.25*VDDIO | V    |

| V <sub>IH</sub> | Input high voltage            |                                        | 0.75*VDDIO | -    | VDDIO+0.3  | V    |

| V <sub>OL</sub> | Output low voltage            | VDDIO = min<br>I <sub>OL</sub> = -2 mA | -          | -    | 0.15*VDDIO | V    |

| V <sub>OH</sub> | Output high voltage           | VDDIO = min<br>I <sub>OH</sub> = -2 mA | 0.85*VDDIO | -    | -          | V    |

| R <sub>PU</sub> | Input pull-up resistance      | VDDIO = typ<br>Vinput = 0 V            | 130        |      | 560        | KΩ   |

| R <sub>PD</sub> | Input pull-down<br>resistance | VDDIO = typ<br>Vinput = 1.1 V          | 130        |      | 560        | KΩ   |

# 6.2 Analog related characteristics

#### 6.2.1 SMPS DC characteristics

| Symbol           | Parameter                    | Min. | Тур. | Max. | Unit | Note                |

|------------------|------------------------------|------|------|------|------|---------------------|

| AVDD43_DCV       | SMPS input supply voltage    | 2.8  | 3.3  | 4.3  | V    |                     |

| DCV              | SMPS output                  | 1.74 | 1.84 | 1.94 | V    |                     |

| I <sub>max</sub> | SMPS current limit           | 120  | -    | 500  | mA   |                     |

| I <sub>cc</sub>  | For normal operation current | -    | 20   | 100  | mA   |                     |

| $\Delta V_PWM$   | Ripple of PWM mode           | -    | -    | 40   | mV   | With L=1uH, C=4.7uF |

| $\Delta V_PFM$   | Ripple of PFM mode           | -    | -    | 90   | mV   | With L=1uH, C=4.7uF |

| l <sub>q</sub>   | Quiescent current            | -    | 50   | 65   | uA   |                     |

#### 6.2.2 TCXO LDO DC characteristics

| Symbol           | Parameter                        | Min. | Тур. | Max. | Unit | Note                                       |

|------------------|----------------------------------|------|------|------|------|--------------------------------------------|

| AVDD43_VBAT      | TCXO LDO input supply<br>voltage | 2.8  | 3.3  | 4.3  | V    | Will change to bypass mode under 3.1 volts |

| AVDD28_TLDO      | TCXO LDO output                  | 2.71 | 2.8  | 2.89 | V    |                                            |

| I <sub>max</sub> | TCXO LDO current limit           | 60   | -    | 250  | mA   |                                            |

| I <sub>cc</sub>  | For normal operation current     | -    | 1    | 50   | mA   | Not include external devices               |

|                  | PSRR-30 KHz                      | 35   | -    | -    | dB   | Co = 1 uF, ESR =<br>0.05, Iload = 25 mA    |

|                  | Load regulation                  | -84  | 10   | 84   | mV   |                                            |

MediaTek Confidential

© 2012 MediaTek Inc.

Page 24 of 35

| Symbol         | Parameter         | Min. | Тур. | Max. | Unit | Note |

|----------------|-------------------|------|------|------|------|------|

| l <sub>q</sub> | Quiescent current | -    | 50   | 65   | uA   |      |

#### 6.2.3 TCXO SWITCH DC characteristics

| Symbol           | Parameter                                                          | Min. | Тур. | Max. | Unit | Note |

|------------------|--------------------------------------------------------------------|------|------|------|------|------|

| AVDD_TCXO_S<br>W | TCXO switch output<br>voltage @ TCXO switch<br>input = AVDD28_TLDO | 2.66 | -    | -    | V    |      |

| AVDD_TCXO_S<br>W | TCXO switch output<br>voltage @ TCXO switch<br>input = AVDD28_CLDO | 1.71 | -    | -    | V    |      |

| I <sub>max</sub> | TCXO SWITCH current<br>limit                                       | -    | -    | 30   | mA   |      |

#### 6.2.4 1.1 volts core LDO DC characteristics

| Symbol           | Parameter                          | Min. | Тур. | Max. | Unit | Note |

|------------------|------------------------------------|------|------|------|------|------|

| AVDD28_CLDO      | 1.2 volts LDO input supply voltage | 1.62 | 1.8  | 3.08 | V    |      |

| AVDD11_CLDO      | 1.1 volts LDO output               | 1.05 | 1.12 | 1.2  | V    |      |

| I <sub>max</sub> | 1.1 volts LDO current limit        | 60   | -    | 250  | mA   |      |

| I <sub>cc</sub>  | For normal core operation current  | -    | 15   | 50   | mA   |      |

|                  | Load regulation                    | -    | -    | -    | mV   |      |

| l <sub>q</sub>   | Quiescent current                  | -    | 10   | 20   | uA   |      |

#### 6.2.5 1.1 volts RTC LDO DC characteristics

| Symbol            | Parameter                           | Min. | Тур. | Max. | Unit | Note                                 |

|-------------------|-------------------------------------|------|------|------|------|--------------------------------------|

| AVDD43_RTC        | RTC LDO input supply voltage        | 2    | 4    | 4.3  | V    |                                      |

| AVDD11_RTC        | RTC LDO output                      | 0.99 | 1.1  | 1.21 | V    |                                      |

| I <sub>max</sub>  | RTC LDO current limit               | -    | -    | -    | mA   |                                      |

| I <sub>cc</sub>   | For normal RTC operation<br>current | -    | -    | 3    | mA   |                                      |

| l <sub>q</sub>    | Quiescent current                   | -    | -    | 3.5  | uA   |                                      |

| I <sub>leak</sub> | Leakage current                     | 2.2  | 10   | -    | uA   | Including LDO and RTC domain circuit |

#### 6.2.6 32 KHz crystal oscillator (XOSC32)

| Symbol     | Parameter           | Min. | Тур. | Max. | Unit | Note |

|------------|---------------------|------|------|------|------|------|

| AVDD11_RTC | Analog power supply | 0.99 | -    | 1.21 | V    |      |

| Dcyc       | Duty cycle          | -    | 50   | -    | %    |      |

MediaTek Confidential

© 2012 MediaTek Inc.

Page 25 of 35

# 6.3 **RF related characteristics**

#### 6.3.1 DC electrical characteristics for RF part

| Symbol                        | Parameter             | Min. | Тур. | Max. | Unit |

|-------------------------------|-----------------------|------|------|------|------|

| I <sub>cc</sub> (GPS-ONLLY)   | Total supply current: | -    | TBD  | TBD  | mA   |

| I <sub>cc</sub> (GPS+GALILEO) | Total supply current: | -    | TBD  | -    | mA   |

| Icc(GPS+BEIDOUu)              | Total supply current: | -    | TBD  | -    | mA   |

| I <sub>cc</sub> (GPS+GLONASS) | Total supply current: | -    | -    | TBD  | mA   |

#### 6.3.2 RX chain (GPS-ONLY)

| Parameter                        | Condition                                                                                              | Min. | Тур.         | Max. | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------------|------|--------------|------|------|

| RF input frequency               |                                                                                                        | -    | 1575.4       | -    | MHz  |

| LO frequency                     | LO frequency is 4.092MHz lower than RF                                                                 | -    | 1571.3       | -    | MHz  |

| LO leakage                       | Measured at balun matching network<br>input at LNA high gain                                           | -    | -70          | -    | dBm  |

| Input return loss                | Single-ended input and external matched to $50\Omega$ source using balun matching network for all gain | -10  | -            | -    | dB   |

| Gain (Av)                        | High current mode with max PGA gain                                                                    | 80   | 78           | 76   | dB   |

| (integrated average over Fc+-4M) | Low current mode with max PGA gain                                                                     | -    | -            | 58   | dB   |

| PGA Gain range                   |                                                                                                        | -    | 24           | -    | dB   |

| PGA Gain step                    |                                                                                                        | -    | 2            | -    | dB   |

| Gain compression                 | Blocker -25dBm CW at 1710MHz,<br>relative to uncompressed gain, max<br>PGA gain                        | -    | 1            | 2    | dB   |

| NF                               | High current mode with max PGA gain                                                                    | -    | TBD          | -    | dB   |

|                                  | Low current mode with max PGA gain                                                                     | -    | 4.8          | -    | dB   |

| ∆NF at Gain=62dB                 | relative to NF at max Gain                                                                             | -    | 0.5          | 1    | dB   |

| ∆NF at Gain=52dB                 | relative to NF at max Gain                                                                             | -    | 2            | 3    | dB   |

| NF under compression             | Blocker -25dBm CW at 1710MHz, max gain                                                                 | -    | 7            | 10   | dB   |

| Input IP3, inband                | max gain, 5M/10M offset@-60dBm                                                                         | -35  | -30          | -    | dBm  |

| Input IP3, outband               | max gain, ~2000M/2400M@-40dBm                                                                          | -15  | -10          | -    | dBm  |

| Input IP2, outband               | max gain, ~800M/2400M@-40dBm                                                                           | +30  | +35          | -    | dBm  |

| Input P1 dB, inband              | PGA gain=0dB, offset 500 k                                                                             | -58  | -55          | -    |      |

|                                  | At offset +-3MHz                                                                                       | -    | -12/-6       | -    |      |

| Frequency                        | At offset +-10MHz                                                                                      | -    | -40/-34      | -    |      |

| response, relative to 4.092MHz,  | At offset +-20MHz                                                                                      | -    | -60/-54      | -    |      |

| (GPS/Galileo)                    | At offset +-100MHz                                                                                     | -    | -100/-<br>94 | -    |      |

| Gain ripple, GPS                 | 4.092+-1MHz                                                                                            | -    | 1.0          | 1.5  | dB   |

MediaTek Confidential

© 2012 MediaTek Inc.

Page 26 of 35

| Gain ripple, Galileo  | 4.092+-2MHz       | -   | 2.0                                                                                                            | 3.0                                                                                                                        | dB   |

|-----------------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|

| Delay ripple, GPS     | 4.092+-1MHz       | -   | 60                                                                                                             | 110                                                                                                                        | ns   |

| Delay ripple, Galileo | 4.092+-2MHz       | -   | 40                                                                                                             | 70                                                                                                                         | ns   |

| Image rejection       | All mode          | -   | 35                                                                                                             | -                                                                                                                          | dB   |

| DC offset             |                   | -   | ±50                                                                                                            | ±100                                                                                                                       | mV   |

| ADC clock             |                   | -   | 16.368                                                                                                         | -                                                                                                                          | MHz  |

| ADC input FS          |                   | -   | 1.0                                                                                                            | -                                                                                                                          | Vppd |

| ADC                   | ENOB              | 7.5 | 8.3                                                                                                            | -                                                                                                                          | bits |

| ADC                   | SNR over Fclk/2   | 45  | $\begin{array}{c cccc} 60 & 110 \\ 40 & 70 \\ 35 & - \\ \pm 50 & \pm 100 \\ 16.368 & - \\ 1.0 & - \end{array}$ | dB                                                                                                                         |      |

| RX Current            | High current mode | -   | TBD                                                                                                            | -                                                                                                                          | mA   |

|                       | Low current mode  | -   | TBD                                                                                                            | 60    110      40    70      35    -      :50    ±100      .368    -      1.0    -      3.3    -      50    -      BD    - | mA   |

### 6.3.3 RX chain (GPS+BEIDOU mode)

| Parameter                           | Condition                                                                                              | Min. | Тур.   | Max. | Unit |

|-------------------------------------|--------------------------------------------------------------------------------------------------------|------|--------|------|------|

| RF input frequency                  |                                                                                                        | -    | 1561   | -    | MHz  |

| LO frequency                        | LO frequency is 4.092 MHz lower than RF                                                                | -    | 1568.2 | -    | MHz  |

| LO leakage                          | Measured at balun matching network input at LNA high gain                                              | -    | -70    | -    | dBm  |

| Input return loss                   | Differential input and external matched to $50\Omega$ source using balun matching network for all gain | -10  | -      | -    | dB   |

| Gain (Av)                           | High current mode with max PGA gain                                                                    | 80   | 76     | 70   | dB   |

| (integrated average<br>over Fc+-4M) | Low current mode with max PGA gain                                                                     | -    | -      | 52   | dB   |

| PGA Gain range                      |                                                                                                        | -    | 24     | -    | dB   |

| PGA Gain step                       |                                                                                                        | -    | 2      | -    | dB   |

| Gain compression                    | Blocker -25dBm CW at 1710MHz,<br>relative to uncompressed gain, max<br>PGA gain                        | -    | 1      | 2    | dB   |

| NF<br>(integrated average           | High current mode with max PGA gain                                                                    | -    | 1.7    | -    | dB   |

| over Fc+-2M)                        | Low current mode with max PGA gain                                                                     | -    | 4.8    | -    | dB   |

| ∆NF at Gain=56dB                    | relative to NF at max Gain                                                                             | -    | 0.5    | 1    | dB   |

| ∆NF at Gain=46dB                    | relative to NF at max Gain                                                                             | -    | 2      | 3    | dB   |

| NF under compression                | Blocker -25dBm CW at 1710MHz, max gain                                                                 | -    | 7      | 10   | dB   |

| Input IP3, inband                   | max gain, +10M/+20M offset @ -<br>70dBm                                                                | -50  | -45    | -    | dBm  |

| Input IP3, outband                  | max gain, ~2000M/2400M@ -40dBm                                                                         | -15  | -10    | -    | dBm  |

| Input IP2, outband                  | max gain, ~800M/2400M @ -40dBm                                                                         | +30  | +35    | -    | dBm  |

| Input P1 dB, inband                 | PGA gain=0dB, offset 500 k                                                                             | -58  | -55    | -    | dBm  |

|                                     | At 0~5MHz                                                                                              | -    | 3      | 4    | dB   |

| Frequency response                  | At 33MHz                                                                                               | -    | -43    | -40  | dB   |

| (relative to 7.16M)                 | At 53MHz                                                                                               | -    | -60    | -57  | dB   |

© 2012 MediaTek Inc.

|                    | At 120MHz                                        | -   | -83  | -80  | dB   |

|--------------------|--------------------------------------------------|-----|------|------|------|

|                    | At 180MHz                                        | -   | -100 | -97  | dB   |

| LPF 3 dB bandwidth | (recom. 4 <sup>th</sup> order Butterworth BW=9M) | -   | TBD  | -    | MHz  |

| Gain ripple        | 7.2+-1MHz                                        | -   | 0.5  | 1.0  | dB   |

| Gain hppie         | 7.2+-2MHz                                        | -   | 1.0  | 2.0  | dB   |

| Delay ripple       | 7.2+-2MHz                                        | -   | 40   | 70   | ns   |

| Image rejection    | All gain mode                                    | -   | 35   | -    | dB   |

| DC offset          |                                                  | -   | ±50  | ±100 | mV   |

| ADC clock          |                                                  | -   | 66   | -    | MHz  |

| ADC input FS       |                                                  | -   | 1.0  | -    | Vppd |

| ADC                | ENOB                                             | 7.5 | 8.3  | -    |      |

| ADC                | SNR over Fclk/2                                  | 45  | 50   | -    | dB   |

| DV Oursent         | High current mode                                | -   | TBD  | -    | mA   |

| RX Current         | Low current mode                                 | -   | TBD  | -    | mA   |

# 6.3.4 RX chain (GPS+GLONASS mode)

| Parameter                        | Condition                                                                                              | Min. | Тур.   | Max. | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------------|------|--------|------|------|

| RF input frequency               |                                                                                                        | -    | 1575.4 | -    | MHz  |

| LO frequency                     |                                                                                                        | -    | 1588.6 |      | MHz  |

| LO leakage                       | Measured at balun matching network input at LNA high gain                                              | -    | -70    | -    | dBm  |

| Input return loss                | Differential input and external matched to $50\Omega$ source using balun matching network for all gain | -10  | -      | -    | dB   |

| Gain (Av)                        | High current mode with max PGA gain                                                                    | 80   | 76     | 70   | dB   |

| (integrated average over Fc+-4M) | Low current mode with max PGA gain                                                                     | -    | -      | 52   | dB   |

| PGA Gain range                   |                                                                                                        | -    | 24     | -    | dB   |

| PGA Gain step                    |                                                                                                        | -    | 2      | -    | dB   |

| Gain compression                 | Blocker -25dBm CW at 1710MHz,<br>relative to uncompressed gain, max<br>PGA gain                        | -    | 1      | 2    | dB   |

| NF (integrated                   | High current mode with max PGA gain                                                                    | -    | 1.7    | -    | dB   |

| average over Fc+-<br>4M)         | Low current mode with max PGA gain                                                                     | -    | 4.8    | -    | dB   |

| ∆NF at Gain=56dB                 | relative to NF at max Gain                                                                             | -    | 0.5    | 1    | dB   |

| ΔNF at Gain=46dB                 | relative to NF at max Gain                                                                             | -    | 2      | 3    | dB   |

| NF under compression             | Blocker -25dBm CW at 1710MHz, max gain                                                                 | -    | 7      | 10   | dB   |

| Input IP3, inband                | max gain, +10M/+20M offset@-<br>70dBm                                                                  | -50  | -45    | -    | dBm  |

| Input IP3, outband               | max gain, ~2000M/2400M@-40dBm                                                                          | -15  | -10    | -    | dBm  |

| Input IP2, outband               | max gain, ~800M/2400M@-40dBm                                                                           | +30  | +35    | -    | dBm  |

| Input P1 dB, inband              | PGA gain=0dB, offset 500 k                                                                             | -58  | -55    | -    | dBm  |

| Eroqueney response               | At 0~23MHz                                                                                             | -    | 3      | 4    | dB   |

| Frequency response               | At 33MHz                                                                                               | -    | -25    | -22  | dB   |

© 2012 MediaTek Inc.

| (relative to 13.14M) | At 53MHz                                             | -   | -43    | -40  | dB   |

|----------------------|------------------------------------------------------|-----|--------|------|------|

|                      | At 120MHz                                            | -   | -66    | -63  | dB   |

|                      | At 180MHz                                            | -   | -85    | -82  | dB   |

| LPF 3 dB bandwidth   | (recom. 4 <sup>th</sup> order Butterworth<br>BW=15M) | -   | TBD    | -    | MHz  |

| Coin rinnlo          | 13+-1MHz                                             | -   | 0.5    | 1.0  | dB   |

| Gain ripple          | 13+-4MHz                                             | -   | 2.0    | 3.0  | dB   |

| Delay ripple         | 13+-4MHz                                             | -   | 10     | 14   | ns   |

| Image rejection      | All gain mode                                        | -   | 35     | -    | dB   |

| DC offset            |                                                      | -   | ±50    | ±100 | mV   |

| ADC clock            |                                                      | -   | 66.192 | -    | MHz  |

| ADC input FS         |                                                      | -   | 1.0    | -    | Vppd |

|                      | ENOB                                                 | 7.5 | 8.3    | -    | Bits |

| ADC                  | SNR over Fclk/2                                      | 45  | 50     | -    | dB   |

| DV Oursest           | High current mode                                    | -   | TBD    | -    | mA   |

| RX Current           | Low current mode                                     | -   | TBD    | -    | mA   |

# 6.3.5 Crystal oscillator (XO)

| Symbol            | Parameter                  | Min. | Тур.   | Max. | Unit |

|-------------------|----------------------------|------|--------|------|------|

| F <sub>tcxo</sub> | TCXO oscillation frequency | 12.6 | 16.368 | 40   | MHz  |

| V <sub>tcxo</sub> | TCXO output swing          | 0.8  | 1.2    | -    | Vpp  |

# 7 Interface Characteristics

# 7.1 RS-232 interface timing

| Baudrate required<br>(bps) | Programmed baudrate<br>(bps) | Balldrate error (%) |         |

|----------------------------|------------------------------|---------------------|---------|

| 4,800                      | 4,800.000                    | 0.0000              | 0.002   |

| 9,600                      | 9,600.000                    | 0.0000              | 0.002   |

| 14,400                     | 14,408.451                   | 0.0587              | 0.0567  |

| 19,200                     | 19,164.319                   | 0.0587              | 0.0567  |

| 38,400                     | 38,422.535                   | 0.0587              | 0.0567  |

| 57,600                     | 57,633.803                   | 0.0587              | 0.0567  |

| 115,200                    | 115,267.606                  | 0.0587              | 0.0567  |

| 230,400                    | 230,535.211                  | 0.0587              | 0.0567  |

| 460,800                    | 454,666.667                  | -1.3310             | -1.3330 |

| 921,600                    | 909,333.333                  | -1.3310             | -1.3330 |

Notes:

- 1. UART baud-rate settings with UART\_CLK frequency = 16.368 MHz (UART\_CLK uses the reference clock of the system).

- 2. The baudrate error is optimized. Each baudrate needs to adjust counter to obtain the optimized error.

- 3. Suppose TCXO frequency is exactly at 16.368 MHz. If TCXO has 20 PPM, the error will raise slightly.

#### Figure 7-1: Timing diagram of RS-232 interface

# 7.2 SPI interface timing

| Description     | Symbol | Min.      | Max.      | Unit | Note |

|-----------------|--------|-----------|-----------|------|------|

| SCS# setup time | T1     | 0.5T      | -         | ns   | 1    |

| SCS# hold time  | T2     | 0.5T      | -         | ns   | 1    |

| SO setup time   | Т3     | 0.5T – 3t | 0.5T - 2t | ns   | 1, 2 |

| SO hold time    | T4     | 0.5T + 2t | 0.5T + 3t | ns   | 1, 2 |

| SIN setup time  | T5     | 3t        | -         | ns   | 1, 2 |

| SIN hold time   | Т6     | 10        | -         | ns   | 1    |

Notes:

MediaTek Confidential

© 2012 MediaTek Inc.

Page 30 of 35

- 1. The condition of SPI clock cycle (T) is (SPI\_IPLLSPI\_IPLL/12) MHz ~ (rf\_clk/1,020) MHz.

- 2. t indicates the period of SPI controller clock, which is SPISPI\_IPLL clock or rf\_clk.

Figure 7-2: Timing diagram of SPI interface

# 7.3 I2C interface timing

| Symbol | Period                         |

|--------|--------------------------------|

| T1     | (MM_CNT_PHASE_VAL0+1)/TCXO_CLK |

| T2     | (MM_CNT_PHASE_VAL1+1)/TCXO_CLK |

| Т3     | (MM_CNT_PHASE_VAL2+1)/TCXO_CLK |

| T4     | (MM_CNT_PHASE_VAL3+1)/TCXO_CLK |